КомпьютерПресс №3 1993. А. Борзенко

Архитектура микропроцессора Intel 80486

Интегральная схема микропроцессора i80486 была анонсирована фирмой Intel в

1989 году на выставке Comdex в Чикаго. И хотя, очевидно, нам не долго уже

осталось ждать появления нового 586-го микропроцессора, на сегодняшний

день одним из самых мощных универсальных микропроцессоров является i80486.

Интегральная схема микропроцессора i80486 была анонсирована фирмой Intel в

1989 году на выставке Comdex в Чикаго. И хотя, очевидно, нам не долго уже

осталось ждать появления нового 586-го микропроцессора, на сегодняшний

день одним из самых мощных универсальных микропроцессоров является i80486.

Архитектура микропроцессора i80486

«В архитектуре взаимосвязаны функциональные, технические и эстетические

начала — польза, прочность, красота».

(Из словаря)

Микропроцессор i80486 достойный продолжатель семейства i80x86‚ поскольку он позволяет создавать вычислительные системы намного более производительные, чем, предположим, на микропроцессоре i80386. В принципе микросхема i80486 состоит из полного микропроцессора i80386, арифметического сопроцессора i80387 и контроллера кэш-памяти i82385. Понятно, что речь не идет о механическом соединении функциональных устройств на одном кристалле. Высокая степень интеграции (более миллиона транзисторов) — это не просто технологическое достижение, а возможность реализовать новые архитектурные решения, которые позволяют повысить производительность микропроцессора. Так, например, в микропроцессоре i80486 используется конвейерная обработка команд, достаточно широко применяемая в RISC-процессорах. При одной и той же тактовой частоте с i80386 микропроцессор i80486 работает в три-четыре раза производительнее. Это связано с уменьшением количества циклов (тактов), необходимых для выполнения команды (инструкции).

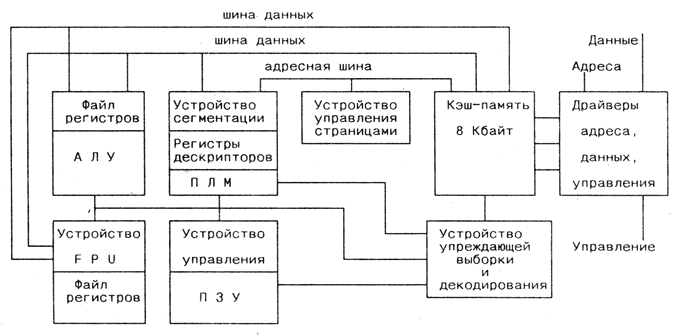

Три в одном

На рис. 1 приведена примерная блок-схема микропроцессора i80486, на которой достаточно легко выделить его основные функциональные узлы — устройство управления памятью (Memory Management Unit, MMU), модуль арифметического сопроцессора (Floating Point Unit, FPU) и блок кэш-памяти (Cache Unit). Несмотря на то, что микропроцессор i80486 обладает всеми свойствами, присущими i80386, имеются, конечно, и различия. Например, в набор команд микропроцессора i80486 наряду с известными инструкциями для i80386, включено несколько дополнительных команд. Однако устройство управления памятью MMU полностью совместимо с аналогичным устройством в i80386. То же можно сказать и о FPU. А это, вообще говоря, означает, что все программное обеспечение, работающее на серии микропроцессоров 80x86/80x87, без внесения каких-либо изменений будет работать и на i80486.

Устройство управления памятью MMU состоит в свою очередь из устройства сегментации (Segmentation Unit) и устройства управления страницами (Paging Unit). Благодаря делению памяти на сегменты (сегментации) коды программ и области данных могут находиться практически в любом месте логического адресного пространства. Иными словами, при сегментной организации памяти каждый модуль занимает свою собственную сплошную область памяти, тогда как при страничной организации модуль разбивается на отдельные страницы. В свою очередь, устройство управления страницами позволяет реализовать механизм страничной организации памяти, который функционирует на более низком уровне и является прозрачным по отношению к процессу сегментации. Это дает возможность управления физическим адресным пространством. Следует также отметить, что страничная организация памяти (paging) может быть отключена чисто программным способом.

Каждый сегмент памяти может подразделяться на один или несколько 4-Кбайтных блоков. А память, в свою очередь, может быть организована в виде одного или нескольких таких сегментов, размер которых может достигать 4 Гбайт. Причем каждому такому сегменту могут придаваться соответствующие атрибуты, которые определяют его расположение в памяти, величину, вид (стек, код, данные) и характеристику защиты. Каждая задача, выполняемая на i80486, может в принципе состоять из 16 381 сегмента, по 4 Гбайта каждый. Таким образом, диапазон виртуальной адресации достигает 64 Тбайт. Устройство сегментации микропроцессора поддерживает четыре механизма защиты приложений и системного режима друг от друга. Благодаря этому на базе микропроцессора i80486 возможно построение высокозащищенных систем.

Принципиально микропроцессор i80486 имеет два режима работы: реальный режим (Real Mode, иначе 8086-Mode) и защищенный (Protected Mode). При этом в реальном режиме он ведет себя просто как очень быстрый микропроцессор i8086. Из этого режима i80486 может легко переключиться в защищенный режим, в котором имеются богатые возможности управления памятью. Например, в этом режиме возможно переключение с одной задачи на другую, причем их обработка будет происходить как обработка независимых задач на своих i8086 микропроцессорах (режим «виртуальных 8086-машин»). Такое название связано с тем, что каждая задача ведет себя таким же образом, как если бы она выполнялась на собственном процессоре i8086 (соответственно i8088).

Устройство арифметического сопроцессора в i80486 работает параллельно с АЛУ и поддерживает большое количество арифметических команд для различных типов операндов. Это, в частности, многочисленные трансцендентные функции, такие как синус, косинус, тангенс, логарифм и т.д. Нужно отметить, что FPU полностью поддерживает стандарт ANSI/IEEE 754-1985 на арифметические операции с плавающей точкой.

Размер внутренней кэш-памяти микропроцессора i80486 составляет 8 Кбайт. Сразу следует сказать, что для некоторых приложений такой размер кэш-памяти вовсе не достаточен. Это касается в первую очередь САПР и настольных издательских систем. Однако в этом случае при разработке соответствующей системы можно воспользоваться кэш-контроллером i82485 и внешней кэш-памятью объемом 64 или 128 Кбайт. Внутренняя кэш-память выполнена как ассоциативная и работает в режиме write through (то есть данные заносятся одновременно и в кэш-память, и в ОЗУ). Кэш в микропроцессоре i80486, безусловно, имеет и некоторые особенности. В частности, страницы памяти могут быть обозначены либо как «кэшируемые», либо как «некэшируемые», причем такое обозначение можно вводить как аппаратно, так и программно. Впрочем, даже само устройство кэша может быть также отключено как аппаратно, так и программно. По некоторым оценкам, использование встроенной кэш-памяти экономит до 80% времени, необходимого для обращения к ОЗУ.

Регистры, регистры, регистры...

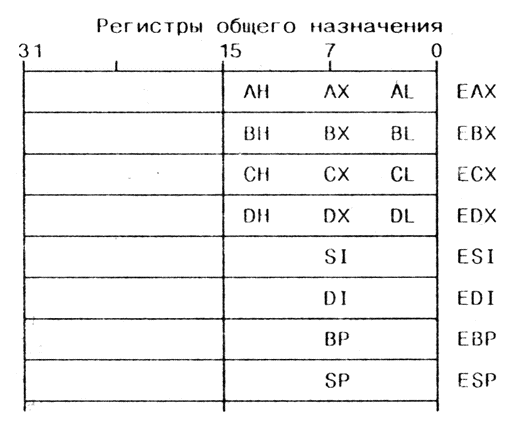

Микропроцессор i80486 содержит, конечно, все регистры, имеющиеся в микросхемах i80386 и i80387. Регистры рассматриваемого микропроцессора можно условно подразделить на три большие группы: базовые регистры, регистры системного уровня и регистры плавающей точки. Рассмотрим эти группы регистров несколько подробнее.

Программная модель i80486 определяется главным образом базовыми регистрами, которые приведены на рис. 2. Это — восемь 32-разрядных регистров общего назначения, которые могут работать с операндами данных размерами 1, 2 и 4 байта или полями бит от 1 до 32. Однако операнды адреса могут иметь длину только либо 2, либо 4 байта. Эти 32-разрядные регистры обозначаются как EAX, EBX, ECX, EDX, ESI, EDI, EBP и ESP. Обозначения двух младших байт этих регистров пользователям микропроцессоров i8088/86/286 уже хорошо известны. Конечно, это — AX, BX, CX, DX, SI, DI, BP и SP. Причем следует отметить, что при доступе к старшим двум байтам этих 32-разрядных регистров содержимое двух младших байтов не изменяется. Этим обуславливается совместимость сверху-вниз с микропроцессором i80286. Операции с байтовыми операндами (старший и младший байты) доступны только для четырех регистров AX, BX, CX, DX, причем старшие байты соответствуют обозначениям AH, BH, CH и DH, а младшие — AL, BL, CL и DL.

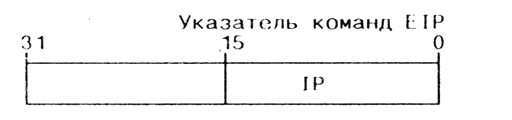

Регистр указателя команд (Instruction Pointer, EIP) — также 32-разрядный и указывает на следующую выполняемую команду, конечно же, косвенно. Этот регистр указывает только смещение относительно начала кодового сегмента адреса, который образуется с использованием содержимого регистра CS и элемента дескрипторной таблицы (подробнее об этом несколько позже). Два младших байта регистра EIP соответствую 16-разрядному регистру IP, который используется только при 16-битной адресации.

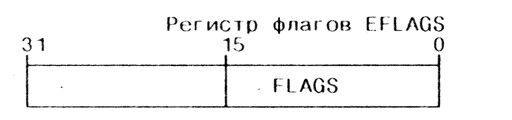

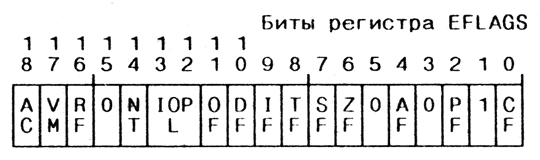

Для обозначения базового 32—разрядного регистра побитной индикации состояния процессора используется так называемый регистр флагов — EFLAGS. Этот регистр содержит биты, характеризующие последнюю выполненную процессором операцию, и некоторую другую служебную информацию. На рис. 3 приведены обозначения битов в регистре EFLAGS. Поясним назначение некоторых из них. Если в регистре EFLAGS установлен 17-й бит — VM (Virtual 8086 Mode), то микропроцессор i80486 переходит в режим «виртуальных 8086-машин». Конечно, это возможно только в защищенном режиме. Бит 16 — RF (Resume Flag) используется обычно для отладочных режимов. При его установке прерывание, вызванное фатальной ошибкой, игнорируется и выполняется переход на следующую инструкцию. Бит 14 — NT (Nested Task) используется в i80486 для наблюдения за несколькими прерванными или вызванными по инструкции CALL программами. Два бита 12 и 13 IOPL (Input/Output Privilege Level) определяют право доступа в защищенном режиме к инструкциям ввода-вывода.

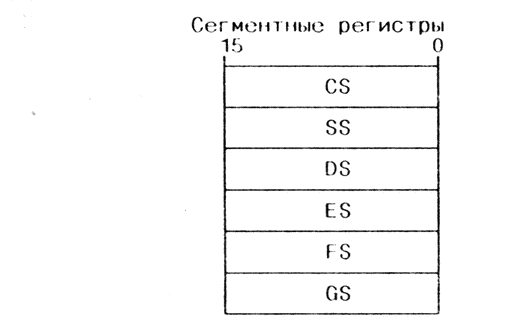

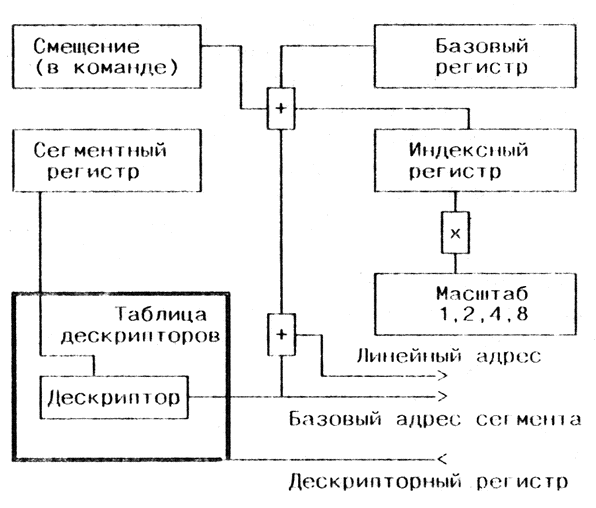

Из шести 16-разрядных сегментных регистров четыре (DS, ES, FS и GS) называются регистрами сегментов данных, CS — регистром кодового сегмента, а SS — регистром сегмента стека. Как работают эти регистры в режиме микропроцессора i8086, достаточно хорошо известно. Для получения 20-разрядного физического адреса необходимо суммировать 16-битное смещение с базовым адресом, хранящимся в одном из сегментных регистров. Причем сложение происходит так, что содержимое сегментного регистра сдвинуто относительно второго слагаемого (смещения) влево на 4 разряда. То есть, по сути, происходит сложение 20-битового базового адреса (4 младших разряда которого, безусловно, всегда нули) с 16-битовым смещением, в результате, конечно, получается необходимый 20-разрядный адрес. При работе же микропроцессора i80486 (ну и, разумеется, i80386) в защищенном режиме исполнительный физический адрес образуется несколько иначе. Можно сказать, что он образуется из пяти компонент. Прежде всего отметим, что в защищенном режиме сегментные регистры называются селекторными, или просто селекторами. Селекторный регистр указывает на соответствующий элемент в одной из Дескрипторных Таблиц, расположенных в памяти. Причем базовый адрес этой Таблицы хранится либо в регистре Глобальной Дескрипторной Таблицы, либо в регистре Локальной Дескрипторной Таблицы, хотя в общем случае может храниться и в ином регистре микропроцессора. Каждый элемент Дескрипторной Таблицы содержит базовый адрес определенного сегмента, его величину и права доступа. У i80486 элемент Глобальной Дескрипторной Таблицы имеет размер 8 байт и состоит из 32-разрядного базового адреса, 20-разрядного поля размера сегмента и атрибутов дескриптора. В поле размера сегмента, например, может храниться либо количество байт (до 1 Мбайта), которое содержит данный сегмент, либо количество страниц по 4096 байт каждая. Следовательно, размер сегмента в защищенном режиме может варьироваться от 1 байта до 4 Гбайт. Таким образом, результирующий адрес в защищенном режиме может быть образован в общем случае суммированием содержимого базового регистра с содержимым индексного регистра, умноженного на масштабный коэффициент (1, 2, 4 или 8), плюс смещение в самой команде и плюс базовый адрес сегмента из элемента Дескрипторной Таблицы (рис. 4).

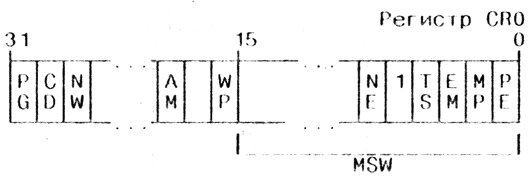

Микропроцессор i80486 имеет три управляющих регистра (Control Registers) системного уровня — CR0, CR2, и CR3 (регистр CR1 зарезервирован фирмой Intel для дальнейшего расширения). В регистре CR0 из имеющихся 32 бит для целей управления и определения статуса используется только 10 (рис. 5). Причем 5 из этих 10 бит появились только в i80486 (в i80386 их нет). Это биты — CD, NW, AM, WP и NE. Функционально все эти 10 бит характеризуют следующее: режимы микропроцессора i80486 — PG, PE, режимы встроенного устройства кэш-памяти — CD, NW, встроенное устройство управления плавающей арифметикой — TS, EM, MP и NE, управление контролем выравнивания — AM, защита записи супервизора — WP. Младшее слово регистра CR0 используется также в качестве статусного слова (слова состояния) микропроцессора (Machine Status Word, MSW), для того чтобы сохранить совместимость с защищенным режимом i80286. Следовательно, команды LMSW и SMSW (Load MSW, Store MSW) действуют только для нижних 16 бит CR0 и игнорируют новые биты. Для того чтобы можно было работать с этими новыми битым, в набор команд микропроцессора i80486 включена специальная инструкция MOV CR0, Reg.

В управляющем регистре CR2 накопится адрес, по которому появилась ошибка при разбиении памяти на страницы. Управляющий регистр CR3 используется только тогда, когда в регистре CR0 установлен бит PG. В этом случае регистр содержит базовый адрес таблицы страниц, которые может использовать микропроцессор для каждой задачи. Сама же эта таблица всегда выровнена на одну страницу (4 Кбайт).

Четыре адресных системных регистра в микропроцессорах i80386/486 используются для таблиц или сегментов, которые хранятся в основной памяти. Это — Глобальная Дескрипторная Таблица (Global Descriptor Table, GDT), Локальная Дескрипторная Таблица (Local Descriptor Table, LDT), Дескрипторная Таблица Прерываний (Interrupt Descriptor Table, IDT) и Сегмент Состояния Задачи (Task State Segment, TSS). Для обозначений соответствующих регистров используются аббревиатуры — GDTR, LDTR, IDTR и TR. Регистры GDTR и IDTR содержат 32-разрядный базовый адрес, а также 16-разрядную границу для таблиц GDT и IDT. Таблицы GDT и IDT находятся в распоряжении всех задач как глобальные сегменты, в то время как LDT и TSS зависят от конкретной задачи. В регистрах LDTR и TR хранятся 16-разрядные селекторы для выбора LDT и соответственно TSS-дескриптора.

Набор регистров для операций с плавающей точкой включает в себя восемь 80-разрядных регистров данных, 48-разрядные указатели данных и команд, а также 16-разрядные регистры управления, состояния и слова признаков. Поскольку принцип работы FPU полностью соответствует работе i80387, а арифметические сопроцессоры — хорошая тема для отдельного разговора, подробно останавливаться на эти регистрах мы пока не будем.

В следующих выпусках нашего журнала мы обязательно вернемся к разговору о микропроцессорах фирмы Intel, и не только о них.

А. Борзенко

КомпьютерПресс 3'92

См. также описание семейства процессоров x86.